La frecuencia máxima que un contador ordinario de PLC puede alcanzar, es tan solo de decenas de Hz, dependiendo en gran medida del ciclo de scan. Si la frecuencia de entrada es superior a esta, es necesario utilizar contadores de alta velocidad (HSC), de lo contrario tendríamos perdidas de pulsos con el consecuente error. Por lo general, existen dos tipos de (HSC) implementados en el PLC. El hardware especial ó (HHSC), y el software ó (SHSC) encargado de interrumpir la CPU cuando su estado cambia.

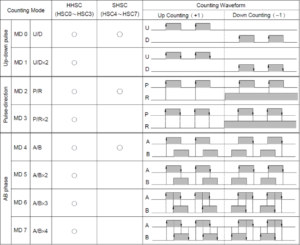

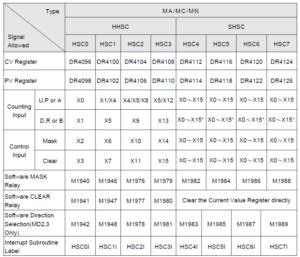

Los PLC FATEK, proporcionan contadores de alta velocidad (HHSC), con sus correspondientes (SHSC). Todos ellos, son contadores de 32-bit de alta velocidad. Como se muestra en la tabla siguiente, cada contador dispone de una serie de modalidades distintas de funcionamiento, que permiten adecuarlos a las necesidades de cada aplicación.

Arquitectura del sistema

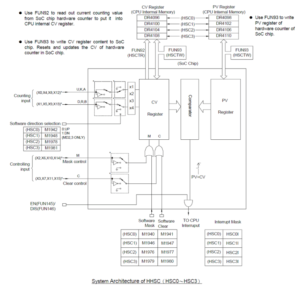

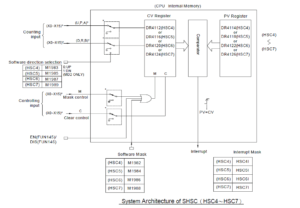

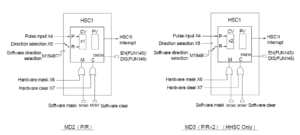

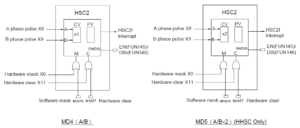

Los siguientes diagramas muestran la arquitectura básica de los (HHSC) y (SHSC), donde se puede apreciar el uso de múltiples entradas y funciones de conteo. Alguna de las funciones, como el número de registro (CV), el número de registro (PV), etiqueta de interrupción, el número de bit para la máscara de software, es propia e inherente a cada contador, los cuales no tienen que ser asignados por el usuario para su configuración. Sin embargo, las funciones marcadas con (*), deben ser configuradas por el usuario mediante la herramienta de programación. Como por ejemplo, (selección de aplicaciones HSC, modo de conteo, definición del uso de las entradas, polaridad inversa).

NOTA: CV = Valor actual, PV = Valor de preselección.

Todas las señales de control de HHSC y SHSC, actúan por defecto, activando en estado ON y desactivando en OFF. Con el fin de cooperar con la polaridad del sensor, las entradas de contaje del HHSC (U, D, P, R, A y B) y las entradas de control (M y C), pueden ser seleccionadas para polaridad inversa.

Por defecto, cuando la señal de control MASK (M) se pone a ON, el HSC será enmascarado y permanecerá sin contar hasta que recupere el estado OFF. CV y PV se mantendrán sin cambios.

Cuando la señal de control CLEAR (C) se pone a ON, el registro CV del contador tomará el valor 0 y quedará inhabilitado el contaje. El HSC comenzará a contar desde 0 cuando (C) regrese al estado OFF.

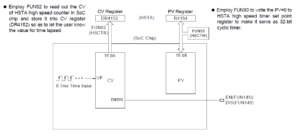

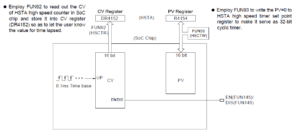

Los HHSC y los SHSC pertenecen a dos circuitos de hardware diferentes, por lo tanto, para mantener la correspondencia entre ambos, sus registros CV y PV deben ser actualizados constantemente. El usuario solo puede acceder a la memoria interna de la CPU, registros CV (DR4096/DR4110), por lo que será necesaria la utilización de la (FUN93) para cargar estos registros. Así como la (FUN92) para leer el valor actual.

Cuando la frecuencia de contaje, o la exigencia de precisión no es excesivamente alta, utilizando la FUN-92 en el programa principal para leer el valor actual de conteo y luego introducir la correspondiente instrucción de comparación, es más que suficiente para realizar un sencillo control de posicionamiento.

Cuando la demanda en el control de posicionamiento es más alta, se utilizará la FUN92 para leer el valor actual del contador, pero no en el programa principal, sino en la rutina de interrupción incorporada para tal efecto. Incorporar en dicha rutina la instrucción de comparación necesaria para realizar el control de posicionamiento.

Cuando la demanda de precisión en el posicionamiento es muy alta, se debe utilizar la función de pre ajuste de interrupción por hardware para contrarrestar el posible desbordamiento. El valor de preselección se puede cargar mediante la FUN-93 en el registro PV de (HHSC). Cuando el valor de CV de (HHSC) alcanza este valor predeterminado, el valor del hardware en (HHSC) le enviará una interrupción a la CPU en el preciso momento en que CV = PV, y saltará en tiempo real a la subrutina donde se establece el control a realizar.

Por otra parte, (SHSC) se utiliza como método de solicitud de interrupción a la CPU, cada vez que aparece un flanco de subida en la entrada de señal. De esta forma la CPU determina si debe aumentar o disminuir el valor del CV. Cada vez que aparece un nuevo pulso, CV es actualizado de forma inmediata. En cuanto la CPU detecta que CV = PV salta la correspondiente interrupción para su procesamiento inmediato. Siempre que se produzca un cambio en el conteo ó entradas de control de (SHSC), la CPU será interrumpida. Cuanto mayor sea la frecuencia de conteo, más tiempo estará ocupada la CPU y por lo tanto, el tiempo de respuesta será más largo, incluso podría ocasionar que el (WATCHDOG) forzará la parada del PLC en casos extremos. Por lo tanto, es conveniente utilizar primero el (HHSC), si fuera necesaria la utilización del (SHSC), la suma de todas las frecuencias de entrada no debe exceder los 8KHz.

Ninguno de los relés especiales de control, como la máscara de software, o control de puesta a cero, funcionan en tiempo real. Esto significa, que aunque aparezca un cambio de estado en alguno de ellos durante el transcurso de la rutina, la señal solo será transmitida al (HSC), después de completar el barrido de la misma y la actualización de entradas y salidas (I/O). Por lo tanto, no es adecuado su uso en aplicaciones donde se precise una respuesta en tiempo real. En cambio su uso es perfectamente válido para realizar la configuración inicial de este, antes de que entre en servicio. Para casos de control en tiempo real, se requiere utilizar las entradas de hardware, o aplicar las siguientes funciones.

FUN-145(EN), FUN-146(DIS), FUN-92(HSCTR), FUN-93(HSCTW).

Cada HSC, puede ser habilitado o deshabilitado mediante el uso de (FUN-145) o (FUN-146). Cuando (SHSC) está desactivado, se deja de contar, pero la función de interrupción permanece activa. Cuando (HHSC) está desactivado, la cuenta sigue funcionando pero la función de interrupción queda desactivada.

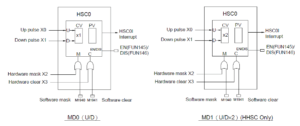

ENTRADAS DE PULSO UP/DOWN. MODOS (MD0, MD1).

Los impulsos introducidos en la entrada (U), provocan un incremento del registro. Los impulsos introducidos en la entrada (D), provocan un decremento del registro. Ambas son entradas independientes sin ningún tipo de relación de fase. Cada una de ellas, incrementa (+1) o disminuye (-1) respectivamente el valor de (CV), cuando el flanco ascendente de la entrada de impulso se produce. Cuando el flanco ascendente de (U) y (D), se producen simultáneamente, se compensaran entre sí. Ambos modos de funcionamiento, incorporan por software las funciones de (MASCARA) y (CLEAR). La función (CLEAR), no está disponible para (SHSC).

Tomando (HSC0) como ejemplo, los diagramas esquemáticos de función para MD0 y MD1, se muestran por separado a continuación.

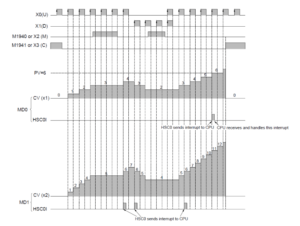

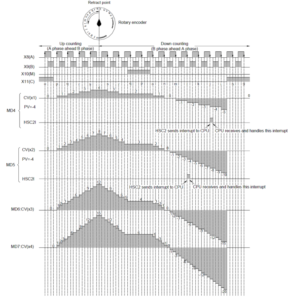

En el siguiente histograma podemos observar el comportamiento real de ambos modos de funcionamiento.

ENTRADAS DE PULSO/DIRECCION. MODOS (MD2, MD3).

En este modo de funcionamiento, el contador tiene una sola entrada de conteo (P), por lo tanto, se precisa de otra entrada (R), para determinar si el contaje será ascendente o descendente. (R=0) ascendente y (R=1) descendente. Para (MD2) se cuentan solo los flancos ascendentes, mientras que (MD3) realiza el contaje de ambos flancos. Los controles de enmascaramiento y puesta a cero, (MASK-CLEAR), se pueden realizar tanto por hardware como por software.

Tomando (HSC1) como ejemplo, los diagramas esquemáticos de función para MD2 y MD3, se muestran por separado a continuación.

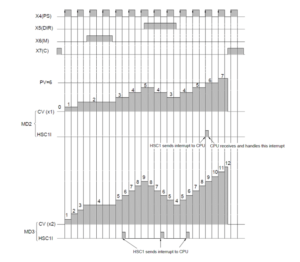

En el siguiente histograma podemos observar el comportamiento real de ambos modos de funcionamiento.

ENTRADAS A-B DESFASADAS. MODOS (MD4, MD5, MD6, MD7).

En este modo de funcionamiento, el contador ofrece dos entradas de contaje (A-B). Para determinar si el contaje será ascendente o descendente, el contador controla el desfase entre ambas entradas. Es decir, si la entrada (A) es detectada antes que la (B), el contaje será ascendente, de lo contrario será descendente.

Las diferencias existentes entre cada uno de ellos, se describen a continuación.

(MD4). El flanco ascendente de (A) incrementa (+1) o (-1) el valor de (CV).

(MD5). El flanco ascendente y descendente de (A) incremente (+1) o (-1) el valor actual del contador. El doble de pulsos que en (MD4).

(MD6). El flanco ascendente y descendente de (A) y el flanco ascendente de (B), incrementa (+1) o (-1) el valor actual del contador. El triple de pulsos que en (MD4).

(MD7). El flanco ascendente y descendente de (A) y (B), incrementan (+1) o (-1) el valor actual del contador. El cuádruple de pulsos que en (MD4).

Tomando (HSC2) como ejemplo, los diagramas esquemáticos de función para MD4, MD5, MD6 y MD7 se muestran a continuación.

En el siguiente histograma, podemos observar el comportamiento real de estos modos de funcionamiento.

PROCEDIMIENTO PARA APLICACIÓN DE UN (HSC. FB-PLC).

1º.- Configurar el modo de funcionamiento del (HSC) y su correspondiente entrada de señal.

2º.- Cableado de la entrada digital de acuerdo con la asignación establecida mediante la configuración del (HSC).

3º.- Establecer el valor inicial de (CV) y el valor de salto a interrupción (PV), en el programa principal. (Main Unit).

4º.- Escriba las acciones necesarias a realizar tras la interrupción y la situación necesaria requerida para próximas interrupciones en el área de subprograma.

5º.- Inicie la operación.

CONFIGURACION. (HSC/HST).

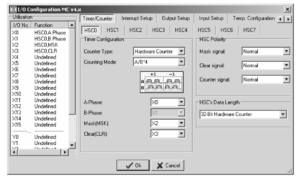

10.4.1 CONFIGURACION DE (HSC/HST) USANDO WINPROLADDER.

Para acceder a la ventana de configuración, desde el árbol del proyecto.

Click (Sistem Configuration) > (I/O Configuration) > (Timer/Counter). Nos muestra la siguiente ventana, donde podremos realizar todas las selecciones que necesitemos.

En la siguiente tabla, podemos observar toda la información relativa al direccionamiento de los elementos auxiliares necesarios para la configuración de estos dispositivos.

FBS-PLC. TEMPORIZADORES DE ALTA VELOCIDAD.

La unidad de temporización mínima de un PLC normal, (BASE DE TIEMPO), solo puede llegar a 1mS. Valor éste, al que habrá que añadir el correspondiente a la desviación producida por el tiempo de exploración. Por lo tanto es necesaria la utilización de temporizadores de alta velocidad (HST), si necesitamos una sincronización más precisa. Por ejemplo la utilización de un (HSC) en cooperación con un (HST) para la medición de frecuencia.

La serie FBS-PLC, está constituida por un temporizador de alta velocidad (HSTA), con una base de tiempo de 0,1mS/16bits y cuatro contadores de alta velocidad de 32-bits (HSC0/HSC3), que pueden funcionar como temporizadores de alta velocidad (HST0/HST3), con una base de tiempo de 0,1mS/32bits. Por lo tanto la serie FBS-PLC puede tener hasta cinco temporizadores de alta velocidad.

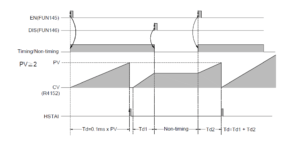

Como sucedía con los (HSC) y sus correspondientes interrupciones, todo (HST) puede ser habilitado o no, mediante las instrucciones (FUN-145) y (FUN-146) como se describe a continuación.

La mejor base de tiempos que podemos obtener en la mayoría de los PLC, supera los 10mS. Aunque muchos de ellos incluyen temporizadores de 1mS, al sumarle el tiempo de exploración obtenemos siempre bases de tiempo muy superiores. Por lo tanto este tipo de temporizadores convencionales, no pueden ser utilizados en aplicaciones de sincronización de alta precisión.

Los temporizadores de alta velocidad de la serie FBS-PLC, tienen una base de tiempo de 0,1mS que no se verá afectada por el tiempo de exploración, mediante el uso de sus correspondientes funciones de interrupción. Estas características, pueden proporcionarnos una precisión 100 veces mejor que la de un temporizador convencional.

(HSTA) TEMPORIZADOR DE ALTA VELOCIDAD.

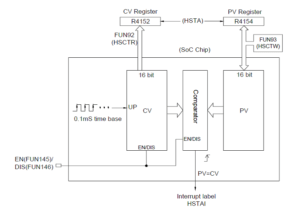

(HSTA) es un temporizador de hardware integrado en el chip SOC. Como en el caso del (HHSC), debe utilizar la instrucción (FUN-93.HSCTW) para cargar el (PV), así como la instrucción (FUN-92.HSCTR) para leer el valor actual (CV). HSTA puede utilizarse de dos modos de funcionamiento diferente. Como temporizador de retraso general de 16-bits, cuando (PV>=2). Como temporizador cíclico de 32-bits, cuando (PV=0).

A.(HSTA) COMO TEMPORIZADOR DE RETARDO 16-BITS.

Después que (HSTA) sea iniciado, el temporizador de retardo se demora durante un tiempo (PV*0,1mS) antes de ejecutar su interrupción. Cuando (PV>0), HSTA funciona como un temporizador convencional de 16-bits y su valor (PV) puede estar comprendido entre (0002H/FFFFH) en hexadecimal. Es decir, el tiempo de retardo se puede establecer entre (0,2mS/6,5535Sg). Salvo que tiene una base de tiempo más precisa y su propia capacidad para ejecutar interrupciones, las aplicaciones de este temporizador son las mismas que las de un temporizador ordinario.

El diagrama siguiente nos muestra la estructura de un (HSTA) siendo utilizado como un temporizador de retardo.

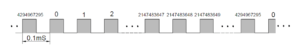

B.(HSTA) COMO TEMPORIZADOR CICLICO DE 32-BITS.

Cuando utilizamos (HSTA) como temporizador cíclico, éste funciona aumentando su valor en 1 cada (0,1mS). Su valor (CV) se desplazará entre (0, 1, 2,…, 4294967295, 0, 1, 2,…). Este temporizador cíclico, cuenta con una base de tiempo de (0,1mS) que incrementará el valor (CV) indefinidamente y retornará a 0 cuando el valor máximo de 32-bits sea superado. Puede ser utilizado para determinar el tiempo que transcurre entre la aparición de dos eventos.

A continuación, se muestra la estructura de un (HSTA) funcionando como temporizador cíclico de 32-bits. Como se muestra en el diagrama, cuando (PV=0) no se produce ninguna interrupción. Para obtener el valor de la temporización, es necesario utilizar la instrucción (FUN-92) para leer el (CV) del chip SOC y guardarlo en el registro de 32-bits (DR4152) del PLC.

La aplicación típica de este temporizador, es la obtención de desviaciones muy precisas en las (RPM) revoluciones por minuto de un motor.

(HST0/HST3). TEMPORIZADORES DE ALTA VALOCIDAD.

Los contadores de alta velocidad (HSC0/HSC3), se pueden configurar como temporizadores de alta velocidad de (32 bits), obteniéndose los referidos (HST0/HST3). Tienen la misma función y base de tiempos que el HSTA a excepción de su capacidad (32 bits en lugar de 16 bits). La configuración de los mismos, se realiza entrando en la pestaña (I/O Configuration > Timer/Counter > Hardware Timer).

—

Puede adquirir nuestros productos en México en la siguiente página https://www.logicbus.com.mx/, en USA y resto del mundo aquí https://www.logicbus.com.

Para contacto directo puede enviar un correo a ventas@logicbus.com o si requiere asesoría soporte@logicbus.com.

Puede llamarnos al +52 33 3854 5975 o iniciar un chat directo en la “burbuja” de la parte inferior, estamos en línea de Lunes a Viernes 08:00 a 18:00 y Sábados de 10:00 a 13:00 horario de México.